|

|

Flip-Flop |

Latch |

|

What is the Basic Principle? |

Edge triggered |

Level triggered |

|

Is it controlled by a Clock Signal? | Yes. | No. |

|

What is it Designed

Using? |

Latches

along with a clock. |

Logic

gates. |

|

What is it Sensitive to? |

Sensitive

to the applied input and the clock signal. |

Sensitive

to the applied input signal- only when enabled. |

|

Speed of operation |

Slow. |

Comparatively

fast. |

|

Classification |

Can

be classified into a synchronous or asynchronous flip-flop. |

NA |

|

Working |

Works

using the binary input and the clock signal. |

Operates

only using binary inputs. |

|

Power

Requirement |

Requires

more power. |

Requires

comparatively less power. |

|

Analysis

of Circuit |

Easy

to perform circuit analysis. |

Analysing

the circuit is quite complex. |

|

Type

of Operation Performed |

Performs

Synchronous operations. |

Performs

Asynchronous operations. |

|

Robustness |

Comparatively

more robust. |

Comparatively

less robust. |

|

Dependency

of Operation |

The

operation relies on the present and past input bits along with the past

output and clock pulses. |

The

operation depends on the present and past input along with the past output

binary values. |

|

Usage

as a Register |

Capable

of working as a register as it contains clock signals in its input. |

Cannot

serve as a register as the register requires further advanced electronic

circuits (EC). Time also plays an essential role here. |

|

Types |

J-K,

S-R, D, and T Flip-flops. |

J-K,

S-R, D, and T Latches. |

|

Area impact |

Requires

more area. |

Requires less area. |

|

Uses |

Constitutes

the building blocks of many sequential circuits such as counters. |

Can

be utilized for designing sequential circuits, but not generally preferred. |

|

Input

and Output |

Checks

the inputs and only changes the output at times defined by any control signal

like the clock signal. |

Responds

to the changes in inputs continuously as soon as it checks the inputs. |

|

Synchronicity |

Synchronous,

works based on the clock signal. |

Asynchronous,

does not work based on the time signal. |

|

Is it fault tolerant? |

Protected

against any fault. |

Responsive

to any occurring faults on the enable pin. |

module d_latch(input d, clk, output q);always @ (clk) beginif (clk)q <= d;endendmodule

module d_latch(input logic d, clk, output logic q);always_latch beginif (clk)q <= d;endendmodulemodule display(input logic signal);// Display the signalendmodulemodule top(input logic input_signal, input logic clk);logic signal_buffer;d_latch latch(signal_buffer, clk, input_signal);display display(signal_buffer);endmodule

entity d_latch isport (d : in std_logic;clk : in std_logic;q : out std_logic);end entity;architecture behavior of d_latch isbeginprocess (clk)beginif rising_edge(clk) thenq <= d;end if;end process;end architecture;entity display isport (signal : in std_logic);end entity;architecture behavior of display isbegin-- Display the signalend architecture;entity top isport (input_signal : in std_logic;clk : in std_logic);end entity;architecture behavior of top issignal signal_buffer : std_logic;beginlatch : entity work.d_latchport map (d => input_signal, clk => clk, q => signal_buffer);display : entity work.displayport map (signal => signal_buffer);end architecture;

module d_ff(input d, clk, reset, output reg q);always @ (posedge clk, negedge reset) beginif (!reset)q <= 0;elseq <= d;endendmodule

module d_ff(input logic d, clk, reset, output logic q);always_ff @(posedge clk, negedge reset) beginif (!reset)q <= 0;elseq <= d;endendmodulemodule display(input logic signal);// Display the signalendmodulemodule top(input logic clk, reset);logic counter = 0;d_ff ff(counter, clk, reset, counter);display display(counter);endmodule

entity d_ff isport (d : in std_logic;clk : in std_logic;reset : in std_logic;q : out std_logic);end entity;architecture behavior of d_ff isbeginprocess (clk, reset)beginif reset = '0q <= '0';elsif rising_edge(clk) thenq <= d;end if;end process;end architecture;entity display isport (signal : in std_logic);end entity;architecture behavior of display isbegin-- Display the signalend architecture;entity top isport (clk : in std_logic;reset : in std_logic);end entity;architecture behavior of top issignal counter : std_logic;beginlatch : entity work.d_ffport map (d => counter, clk => clk, reset => reset, q => counter);display : entity work.displayport map (signal => counter);end architecture;

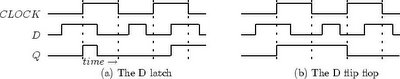

Putting things differently, a latch is a circuit element that can hold a state (either 1 or 0) and remain in that state until a new input signal arrives. A flip-flop, on the other hand, is a type of latch that is designed to change state only when a specific set of conditions is met, such as a clock signal. In other words, a flip-flop is a synchronous device, meaning it changes state only at specific points in time, whereas a latch is an asynchronous device, meaning it can change state at any time. Additionally, flip-flops often have specific inputs for setting and resetting the state, whereas latches typically have a single input that determines the new state.

Flip-flops are synchronous devices that change state only on the rising or falling edge of a clock signal, whereas latches are asynchronous and can change state at any time in response to the input signal.

Inputs:

Flip-flops typically have two inputs, a data input (D) and a clock input (CLK), whereas latches usually have a single input that determines the new state. Some flip-flops may also have a reset input (R) to initialize the circuit to a known state.

Output:

Flip-flops and latches both have two outputs, representing the two possible states (1 or 0). The output of a latch is a direct function of the input, whereas the output of a flip-flop depends on both the data input and the clock edge.

Timing:

Latches are considered to be faster than flip-flops because they don't wait for a clock signal to change state. However, the speed of a flip-flop is more predictable, since it changes state only on the rising or falling edge of a clock signal.

Usage:

Latches are used in applications where the timing of the input signal is not critical, such as in buffer circuits or level-sensitive data storage. Flip-flops are used in synchronous circuits where the timing of the data must be controlled, such as in digital clocks or digital counters.

Types:

There are several types of flip-flops, including SR, D, T, JK, and Master-Slave flip-flops, each with its own set of inputs and outputs, and specific uses in digital circuit design. Latches, on the other hand, come in two main types: SR and D latches.

A common implementation of a flip-flop is a pair of latches (Master/Slave flop).

Latches are sometimes called “transparent latches”, because they are transparent (input directly connected to output) when the clock is high.

The clock to a latch is primarily called the “enable”.

For more information have a look at the picture below.

Latches:

- Use flops, not latches

- Latch-based designs are susceptible to timing problems

- The transparent phase of a latch can let a signal “leak” through a latch — causing the signal to affect the output one clock cycle too early

- It’s possible for a latch-based circuit to simulate correctly, but not work in real hardware, because the timing delays on the real hardware don’t match those predicted in synthesis

- Limit yourself to D-type flip-flops

- Some FPGA and ASIC cell libraries include only D-type flip flops. Others, such as Altera’s APEX FPGAs, can be configured as D, T, JK, or SR flip-flops.

- For every signal in your design, know whether it should be a flip-flop or combinational. Examine the log file e.g. dc shell.log to see if the flip-flops in your circuit match your expectations, and to check that you don’t have any latches in your design.

- Do not assign a signal to itself (e.g. a <= a; is bad). If the signal is a flop, use an enable to cause the signal to hold its value. If the signal is combinational, then assigning a signal to itself will cause combinational loops, which are very bad.

thx

ReplyDeleteThanx,

ReplyDeleteA latch is a level-triggered device and a flipflop is an edge-triggered device.

this just really helped me out thank you!!

ReplyDeleteQuite a important concept , I got screwed for my first interview when i said that both were the same ( i had forgotten ), its not going to happen again

ReplyDeletethnx a lot

ReplyDeleteYes you are right! It's important to call things with it's names...

ReplyDeletethanks. This is a very good clarification. saying that a flip-flop is edge sensitive and latch is level sensitive is not a good enough definition. It must be made clear that when a latch is enabled it becomes transparent while a flip flop's output only changes on the clock edge.

ReplyDeletethanks for the valuable knowledge

ReplyDeleteThere are different ways to answer this question..

ReplyDeletea) A M/S F/F is made of two latches called phi2 and phi1

b) a latch is created from a keeper element fed by a passgate.. the pass gate opens when the enable is clocked .

c) The latch and a edge triggered F/F also have different setup edges..

nice one

ReplyDeletecan ayone tell me why reset is always kept low in cmos logic ckts?

ReplyDeletecan nyone tell me why reset is always kept low in cmos logic ckts

ReplyDeletewhats the design diff for different clk pulse based activation i.e. level or edge?

ReplyDeletethanks, we explained and good advice! Best wishes from Finland!

ReplyDeletethankx

ReplyDeletetnq

ReplyDeleteGreat post! Readers might also enjoy Steve Mackay’s engineering blog at http://www.idc-online.com/Engineering-Blog and the free technical resources available there.

ReplyDelete